Altera版SDRAMC(SOPC BuilderのLibraryのSDRAMC)との性能差を見ることが目的なので、

同じSystem構成でDRAMCがAltera版のものと自作SDRAMC版を生成して動作させることにした。

ただし、新しくSystem構成を考えるのは面倒なのでDE0のDemonstration用Designの一つである

DE0_NIOS_SDCARDを基にしたが、Nios IIはEconomy版に変更した。

自作SDRAMCをSOPCのComponentとして登録する手順としてはまず、Avalon-MM用のWrapper moduleを作成し、次にComponent EditorにHDLをAddして信号やInterface等の設定を行った後、FinishするとComponent Libraryに登録されるので、それをSOPC SystemにAddする。

Wrapper moduleの中身であるが、これは下図のようにほぼ信号名の付け直しで済んだ。

自作SDRAMCを組み込んだSystemが出来たので、合成してsof fileを生成後実機に流し込み、

何がしかのProgramを作成して走らせれば実機での動作確認が出来るが、この方法だと感覚的

にしか違いが判らない気がしたのでまずはSimulationで確認することにした。

まず下図のようなProgramを書いてSimulationしてみた。

このProgramではtext, data, stack等の全てのsectionをonchip_memに配置するようにして、

Programから明示的に読み書きしない限りはSDRAMへのAccessが発生しないようにした。

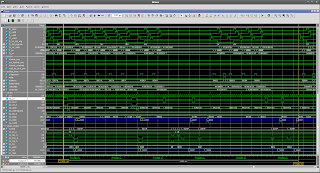

下図はAltera版SDRAMCのSystemでのSimulation波形だ。

SDRAMへのAccessはもっと近接していると思ったら違った。随分スカスカだ。

objdumpを確認したところ、Nios IIをEconomy版にしたためもあると思うが番地計算で

値を4倍するのに加算命令2回で行う等冗長な命令列になっていた。

(Nios IIはShifterは持ってなかったっけか?)

2011/09/20 追記

後にNios IIプロセッサ・リファレンス・ハンドブック(n2cpu_nii5v1_j.pdf)を参照したところ、

Nios II/eコアは「最大で6クロック・サイクルあたり1つの命令を実行」するらしい。

波形を見る限りでは「最大で6クロック」というより「常に6クロック」という感じだが。。。

一方、Nios II/eは最大200MHzまで動作可能という記述もどっかの資料に書いてあったが、

ということは頑張って200MHzで合成できたとしても実質はその1/6の33.333MHzの性能しか

出ないということのようだ。 Nios II/e は。

下図では、SDRAMへの最初のWriteから最後のReadの完了までで2260nsかかっている。

Altera版SDRAMCはAvalon-MM側も16bitであるのに対してNios IIは32bit busなので、

Avalon-MM MasterとSDRAMC間のTransactionは必ず2回発生する。

この2回のTransactionがどういう間隔で発生するのか興味があった。 WriteはData転送を

行うI/F境界で転送が成立した時点でWrite完了と見做せるので連続的に発生できる筈である。

実際波形を見ても、WriteはBurst的になっている。 Readについても、Avalon-MM I/Fは

Split Transaction型のI/Fなので一々Read Dataの到着を待つ必要はなく連続してRead

要求を発行できる筈だ。が、波形をみるとそうなっていない。 1 Transaction毎にRead Data

の戻りを待っている。 Avalon-MM I/FのMaster があまり工夫されていないのだろう。

下図は自作SDRAMCのSystemでのSimulation波形だ。

上記と同様にWrite開始からRead完了までで1761nsだった。

ただし、波形をみてもわかる通りこの方法の場合、SDRAMへのAccessの占める時間は

僅かなのでこの結果を持って性能差を判断することは適切ではないだろう。

そこで、次に下図のようなProgramで且つこのProgram自体もSDRAM上に配置し、

且つStackやData sectionもSDRAM上に配置した状態で動作させてみた。

この状態の方がより現実的だろう。

実行時間としてはSDRAMのAccessが始まる時点から、Nios IIのInstruction busの

Addressがmain関数の最終番地になるまでを見た。(下図のret命令部)

下図がAltera版SDRAMC SystemのSimulation結果だ。

また、下図が自作SDRAMC SystemのSimulation結果だ。

Altera版の実行時間が2msec、自作版が1msecなので性能差は2倍だ。

ただ、これは自作版の方が性能が良いと見るよりは、むしろ、自作版の方が普通であり

Altera版の方が性能が低いと見るべきだろうと思う。なぜならbus幅が16bitと、

内部の1/2のためThroughputが0.5になってしまっているからだ。

(32bit幅のSDRAMを搭載したSystemでは差はないかも知れないし。。。)

DE0のように16bit幅のSDRAMを搭載したSystemでは、自作SDRAMCのようにSDRAM

I/F部を倍速で動かすことでThroughput 1.0を保つことは可能なので、要は工夫次第と

いうことだろう。

最後にsofを実機に流し込んで、SDRAMの全領域のR/W check programを走らせて

Errorにならない事を確認した。また、160MHz駆動版(内部80MHz、SDRAM160MHz)

も作成して動作させてみたがこちらも動作した。

ここまでのRTL一式はいつも通り、

http://www.hi-ho.ne.jp/bravo-fpga/

に置いた。

次はこのSDRAMCをSpartan3Eに実装しよう。

0 件のコメント:

コメントを投稿