金曜日に基板が届いた。 どんな荷姿で届くんだろうと思っていたら、小さい箱だった。

内容物説明が何故かGiftになっている。(チェックが付いている)

早速、開梱

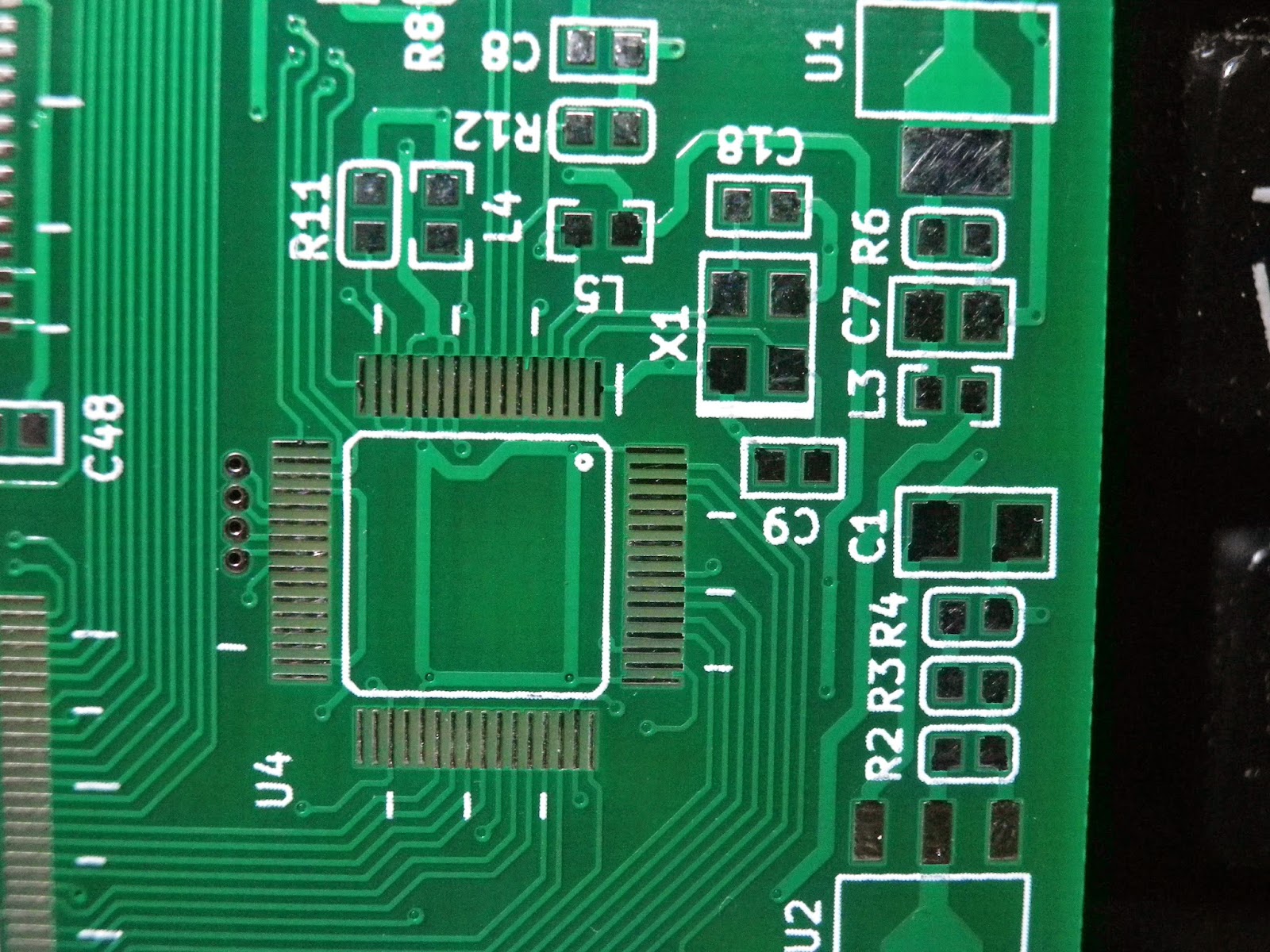

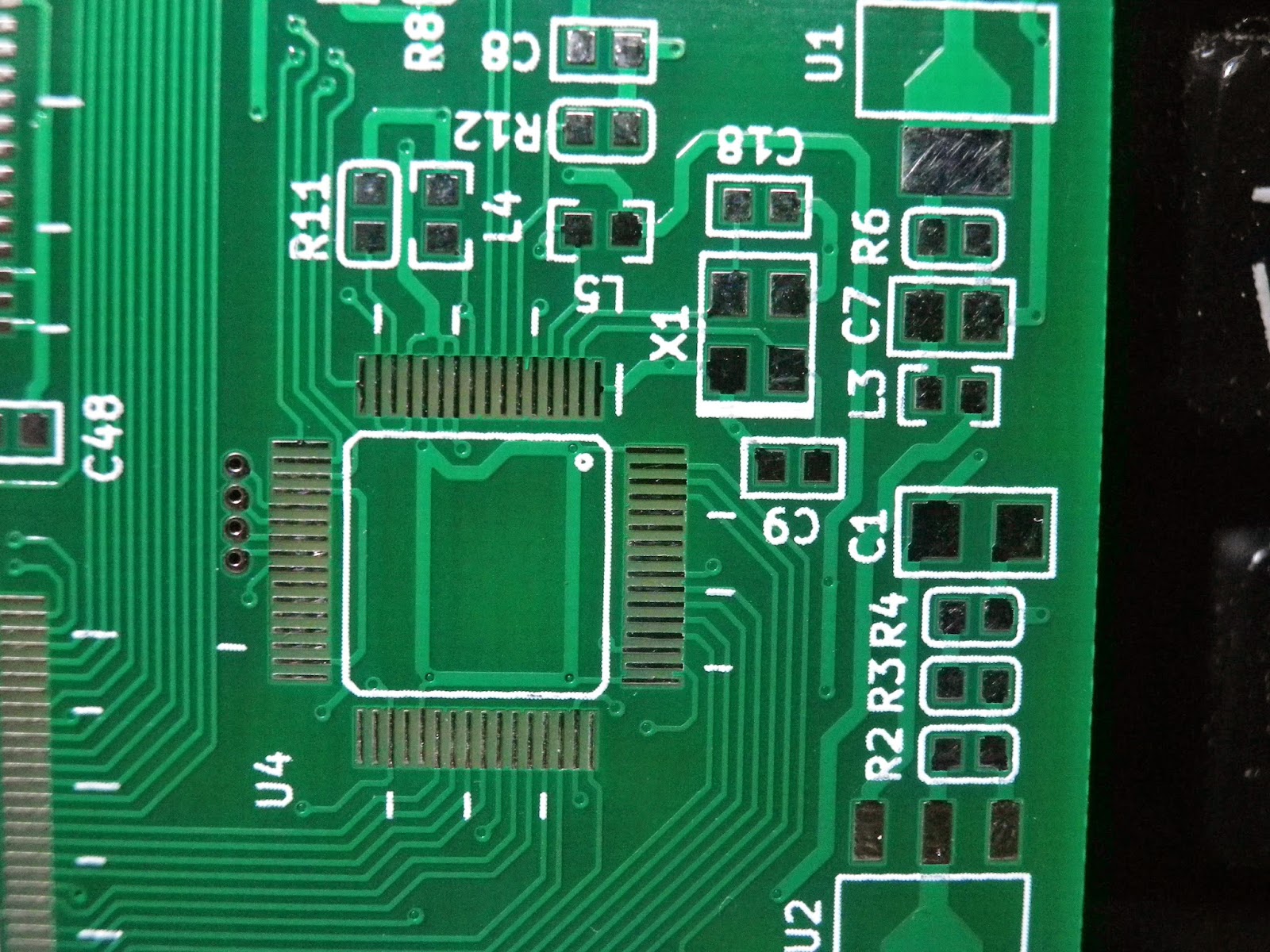

今回は、信号線幅は0.22mm、VIAは0.6mm(ランド径)/0.3mm(穴径)で設計したのだが、パターンは綺麗に仕上がっているようだ。

し、しまった。。。 年数を間違えてた。 orz

シルク印刷は部品面側は綺麗に出来ているのだが、半田面側は滲んでいる部分があった。

全ての基板が同じ訳では無くて良い物もあるので、データ作成の問題では無さそう。多分製造上の問題だろう。

もう1箇所、ミスが発覚してしまった。 写真の真ん中辺にC49があるが、その左隣の部品のReference文字が無い!!! データを確認したところ、これはC47で、Reference文字はC49の枠内に置いてしまっていた。

LatticeのBreakout Boardとの比較

この外形だと、秋月通商で売っているアクリルケースにも収納できる。

Breakout Boardは微妙なところで入らない。

外観検査はこの位にして、部品実装に移った。 QFPやSDRAM等の大きな部品はすぐ実装出来たのだが、C・R類の実装に手間取って結局5時間かかった。

FPGA部 ハンダゴテで手付した割りには、うまく出来ていると思う。

FT2232HL部 少しズレてしまったが、隣接パッドとショートしていないのでこのまま行くことにした。

SDRAM部 ここはピン間ピッチが広いので簡単だった。

USBコネクタ部付近

+5Vの電源を供給して電圧レギュレータ出力を確認した。 (FPGAなblank、USBも繋いでいない状態)

コア電圧(+1.2V) 若干高めだけどまっいっか。

+3.3V

この状態での電流は約40mAだった。 FPGAに回路情報を書いて動作させればもっと多くなる筈。

回路情報をFPGAに書いて動作を見てみた。 これはロジアナの回路のピン配をこの基板用に変更したものだが、LEDを点滅する回路も含んでいるのでまずは、この部分の確認から行う。

FT2232HLのEEPROMがプログラムされていない状態、つまり、DescriptionにLatticeの文字列がない状態でLatticeのツールがちゃんとFPGAにコンフィグデータを書いてくれるか不安だったのだが、大丈夫の様だ。ちゃんと書き込みできた。

LEDはFPGAのINITとDONEピンに接続している。このピンはユーザーI/Oとしても使える。ALTERAの場合は、コンフィグ関連のピンをユーザーI/Oとして使う場合は設定が必要だが、Latticeの場合はDefaultでユーザI/Oとして使え、逆にコンフィグ専用にしたい場合に設定が必要な様である。

動いた。

次に、FT2232HLのEEPROMの書き込みに取り掛かったのだが、EEPROMの購入ミスが発覚した。 FT2232HLに接続するEEPROMは93LC46や56で16bitアクセスできるものでなければならないのだが、間違って8bit専用のものを買ってしまっていた。 仕方ないのでジャンク箱を漁ってみたら16bitタイプの93LC56が載ったジャンクのサウンドカードが出てきたのでそこから取り外して使うことにした。 結果、書き込み出来た。

書き込みデータの一部

FTDIのライブラリを使って書き込むのでプログラムはとてもシンプルだ。

この基板をPCに接続し、Linuxのlsusbコマンドで見ると以下のように見える。

ついでなので、ロジアナも書き込みを行った。

GUIプログラム起動時のPORT SELECTIONでは以下のように表示される。

ということで、ここまでは致命的な問題も無く出来た。 後は、SDRAM周りの動作確認になる。

この基板の部品表は以下の通りで、基板も含めて1枚あたり\4,000以下だ。ただし、C,R等の部品が購入できる数量が大きかったりするので全部の部品を新規に揃える場合はもっと上がることになるだろう。