今時のデバイスだと、うちの子はどの位の周波数までいけるのかを見てみた。

具体的にはCMOD S7というSpartan7を搭載したDigilentの評価ボード向けにデザインを作ってVivadoでインプリしてタイミングエラーにならないギリギリの周波数を探した。

このCMOD S7はxc7s25csga225-1が実装されている。

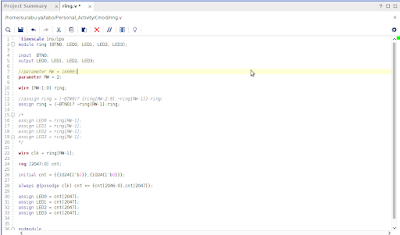

インプリするアーキテクチャは以下のようにした。ZUMI32のペリフェラルはINTC(割り込みコントローラ)、TIMER、GPIO (LED & SW)、命令用メモリは8KByte、データ用メモリは4KBとした。

左側のUARTとUIは命令メモリとデータメモリにプログラムをダウンロードするためのモジュールでありZUMI32からはアクセス出来ない。

タイミングエラーにならないギリギリのクロック周波数を探った結果、上限は113MHzだった。但し、これはFPGAのスピードグレードが-1の場合であり、-2だと140MHzまでmetした。 このデザインはリソース使用率が低く、Physical viewを見るとかなり散らばって配置されているので、もっとリソース使用率が高いデザインにするともう少し上の周波数まで行けるんじゃないだろうか? という気がする。

ZYNQでも同様にしてやってみた。以下のようなアーキテクチャにした。

デバイスはxc7z010clg400-1だ。

このデザインでの上限は100MHzと、驚いたことにSpartan7よりも低い値になった。しかし、physical viewを見ると中身はスッカスカでありこれがクロック周波数を下げている要因では無いかという気がする。

もっと混んだデザインにするとmetする周波数は上がるんじゃないだろうか。

最新のデバイスではないが、Lattice MachXO2でもやってみた。ターゲットデバイスはLCMXO2-7000HC-4TG144Cにした。

結果は49MHzが上限だった。リソースの使用率は30〜40%位だった。スピードグレードを5にした場合は53MHzに上がった。

CMOD S7に戻って、プログラムを作って動かしてみた。CMOD S7には3色LEDが1つ、単色LEDが4つ搭載されているのでタイマー割り込みで単色LEDをナイトライダー風に点滅させるプログラムにした。 フォアグラウンド側はmain()でタイマーの初期設定後、割り込みを許可し、その後 while(1); ループに入る。後はタイマーに設定した周期で割り込みが入るので、割り込みハンドラーでLEDの点滅処理を行う。

このプログラムを-O2最適化オプションでコンパイルして得られたサイズは命令部が1992Byte、データ部(固定値)が24Byteだった。

実機で動かす前にシミュレーションで確認してみる。

※.シミュレーションでは割り込み周期を10usに短縮した。

上図の通りフォアグラウンドは while(1); で無限ループしているので、フォアグラウンド実行時のPC(プログラムカウンタ)は同じ番地を指している。

割り込みを検出すると割り込みベクタアドレス0x00000020をフェッチし、そこから割り込みハンドラに分岐し、処理が終わると割り込み前の番地に戻っている。

実機動作

動作周波数については、ちょっと物足りなさを感じるが全く使い物にならないレベルでは無い。

50MHz以上なら遊びに使うにはまぁまぁ十分ではないかと思う。

プログラム開発は、PC上でCでプログラムを書いてコンパイルして動かすのと同等の手順で出来る。

出来上がったマシン語列は今回のように実機にダウンロードして動かすようにも出来るし、ROM化(命令メモリに初期値として設定)することも出来る。難点はデバッグ用の仕組みをまだ入れていないことだが、今の所特に支障は無い。

このCPUでモーターとかアクチュエータを動かしてみたり、装置のユーザーインタフェース部の処理をさせたりしてみたいもんだ。