DCモーターやHDDのスピンドルモーターや、I2C I/FのA/D、D/A、温度センサやサーミスタ、ペルチェ素子などがあった。やはり人生持つべきものはジャンク箱だ。

DCモーターのPIDによる回転数制御などもやってみたいと考えている。 以下は仮組みした状態。DCモーターの回転数をロータリーエンコーダで測り、PWMでDCモーターを制御する。

この他にも、スピンドルモータの制御やペルチェ素子の制御(温調)などもやってみたいと考えているが、今日は別のことをやってみた。

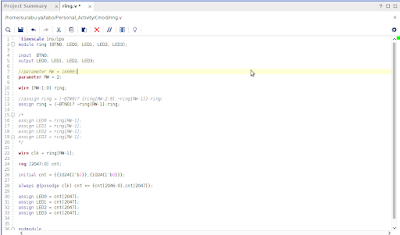

以前、このブログでFPGAでLチカというのをやった。FPGAの中にリングオシレータを作りその出力でLEDを点滅させるというものだ。

これをCMODS7のSpartan7でもやってみた。

Vivadoでこの方法でインプリできるのか興味があったのだが、やってみたらインプリできた。

但し、XDCに set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets BTN0_IBUF] という制約を書く必要があった。

トランスペアレントラッチの数だが、色々と試行した結果、このやり方の場合は14600個が上限だった。CMODS7に搭載されているSpartan7はxc7s25csga225-1で、このデバイスのFF数は29200個だがFFでなくラッチとして使う場合は14600個が上限のようだ。

FFの使用率は50%だがSLICEとしては全部使われている。

得られた出力波形が以下だ。

上記は29188bitのリングカウンタの値を101010.... にしており、これを発振可能な最大周波数で駆動している。このときの消費電流を見たら635mAも流れていた。

素子数を半分にすると406mA、さらに半分にすると239mAになった。電流はUSBの電流を見ている。

周期が15.6usecなので1素子当たりの遅延は単純計算で 15.6/2/14600 ≒ 0.534[nsec] となる。したがって、素子1個のリングオシレータにした場合は約1GHzのクロックが生成できそうだ。

Spartan7のデータシート DS189によるとスピードグレード -1 のCLBのトグル周波数 FTOGは1098MHzとなっているので、ほぼこの値に近い。

リングオシレータを1素子にし、その代わりにそれをGBUFを通してクロックとして2048個のFFによるリングカウンタを駆動して出力が得られるかを見てみたところ出力がトグルしなかった。

次に素子数を2にしてやってみたらこちらは出力された。

周波数は約192.4KHzだった。これの2048倍がクロック周波数になるので 192.4×2048 ≒ 393.2MHzとなった。これはリングオシレータの素子数が2の場合なので、1の場合はこの2倍で786.4MHz。

何故か、最初に求めた値より若干低い。

この場合はリングカウンタを使ったが、このようにラッチではなくFFとして使う場合は上限がカタログ通りのFF数までは使えるようだ。以下のようにリングカウンタのbit数を29188個にしてもインプリできた。インプリ後のUtilizationを見るとFFの数が何故か29194になっていた。

0 件のコメント:

コメントを投稿