Memory R/W TestのProgramを走らせていてPassする度にLEDを点滅させているだけなので面白みにかけるが、以下は動作している様子だ。

Memory Readの為のCalibrationは無しで動作できている。

LPDDR(Mobile DDR)はDLLを内蔵していないため、tACの振れ幅がものすごく大きい。

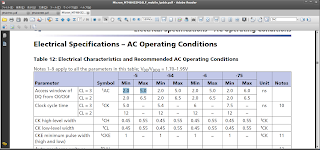

普通のDDRの場合は±700ps位の値だ。

JEDECの規格書から引用

これに対してLPDDRの場合は2.0ns~5.0nsもある。

JEDECの規格書から引用

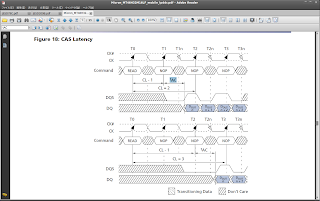

MicronのDatasheetから引用

このtACはClockに対するDQの出力遅延で2.0ns~5.0nsもの振れ幅がある。 勿論動的にjitter的にこの範囲で揺れ動く訳ではないのだろうが、こんだけ幅があるということは、DQをFPGAのIDDRで取り込む場合に、Clockの立上りから取り込みが始まる場合と、立ち下がりからになる場合があるということだ。 以下はMicronのMobile DDR Simulation Modelを使って本SDRAMCをSimulationした波形だ。下がtACが5.0nsの場合で上は2.0nsの場合だ。

波形下部のw_dinはIOBUFの出力、w_din2はIDDR2の出力部だ。 IOBUFとIDDR2間にIODELAY2を置いてこの遅延量を調整(Calibration)しようにも、最大では1Bit期間(2.5ns)以上も遅延させることになり無理が有る。 そこで、本SDRAMCではDQSの値からDataの順序を判定するようにしている。 DQSはH→Lの順に振れるのでHがどのClock Edge側で取り込まれているかで判定をしている。 勿論、DQ、DQSのEdgeがIDDR2のSetup/Holdに引っかかる場合も有り得るので、IODELAY2による遅延調整もできるようにしているが、これはあくまでもSetup/Hold違反の為の調整であって、取り込みEdgeの調整用ではないということだ。

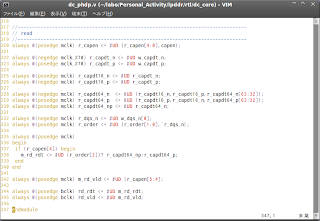

結局PHY_DP部は以下のようになった。

Write系

258行目のfor calibrationはIODELAY2自体のCalibrationの為のState Machineだ。IODELAY2は最初に(あるいは適宜)入力信号(Bit信号)の1期間を教える必要がある。本SDRAMCでは起動時に自動でCalibrationを実行する。また、任意のTimingでSoftwareからこのState Machineを起動することもできる。

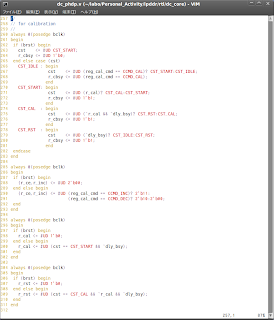

以下はCalibrationの様子。Bit期間を教えればいいので、FPGAからDQとDQSを出力しこれをIDDR側にU Ternさせて調整をさせている。

DQSはmclk、DQはこれに270°位相遅れのmclk_270で駆動している関係で、どちらかを遅らせて位相を合わせる必要があるが、現状はDQSの位相を遅らせている。具体的にはDQS側のIODELAY2のIDELAY_TYPE値をVARIABLE_FROM_HALF_MAXにしている。Calibartion完了後、IODELAY2にRSTを印加するとこの遅延値に設定される。

Read系