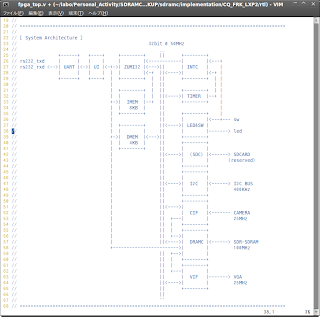

最終的に、FPGAのSystem Architectureの方は下図の様にした。

MPIFを4 portに拡張して、UIF(uart)、CIF(camera)、VIF(vga)、CPU(zumi32)から、DRAMのAccessが出来るようにした。

Memory R/W は問題なさそうだが、SDRAM→VGAの経路に問題があるようでまともに表示されない。 zumiでMemory R/W check programを実行させた結果はOK。 CameraからSDRAMに取り込んだ画像をuart経由で読み出してppm に変換してViewerで確認した結果もOK。 uart経由で画像Dataを書込み、次に読み出して同様にppmに変換してViewerで確認した結果もOKだった。

しかし、vifをenableにしてVGAに出力させると画が出ない。

このvif moduleはDE0でのSDRAMCの動作確認でも使用した物なのでmodule自体に問題は無い筈なのだが??

FPGA内部の帯域も問題無い筈だ。FPGA内部は50MHz, 32bit busなので、50MHz x 4 = 200MByte/sec。 SDRAMはPage切り替えやRefreshがあるので現実的には70%程度として、200M x 0.7 = 140MByte/sec。 一方、vifはVGAでRGB565なので640 x 2 / 25usec = 51MByte/sec。 Cameraは15fpsなのでレートとしてはvifの約半分として合計で51M x 1.5 = 76.8 MByte/sec → 77MByte/sec としても140MByte/sec の半分程度だ。

以下のSimulation波形を見ても十分余裕があるのが判る。

したがって、帯域不足とかそういった問題ではない筈だ。

SDRAMの内容の代わりにColor Barを表示するようにしてみたら、こちらはちゃんと表示された。

したがって、半田付けが失敗している訳ではない。

line bufferか、SDRAMのburst readに問題があるのか?

Simulation上は問題なさそうなんだが。それにDE0での実績もあるし。

う~ん。。。

0 件のコメント:

コメントを投稿