以下のようなアーキテクチャとした。従来であればプログラムダウンロード用のパスも設けるのだが、iCE40LMのEBRAMはtrue dual port ram モードを持っていないため省略した。

合成の結果はP&R(配置配線)でエラーとなってしまった。

iCE40は配線用リソースが少ないと見え、純粋な論理回路としてはLUTやDFFはリソース内に収まっているが、配線経路としてLUTが使用されておりその数と合わせるとデバイスのリソース規模を超過してしまうようだ。

そこで、今度はデバイス設定をiCE40UltraのiCE5LPに変えてやってみたところ成功したが、リソースの使用率は100%で、P&Rに1時間位かかった。

iCE5LPのLUTとBRAMの規模はiCE40LMと同じだが、その他にハードマクロの乗加算器(16x16 Multiply & 32bit Accumulator Blocks)を持っている。 ただし、パッケージはWLCS36 (6x6)とWLCS20 (5x4)である。iCE40LMはWLCS25 (5x5)なので非互換ということになる。

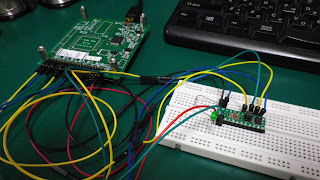

以下の写真の右側がiCE5LPのWLCS36パッケージ品である。こうしてみると大きさ的には大差無いと言える。こいつのハンダ付けも今度挑戦してみようと思う。

iCE40LMに戻って、今度はCAN IPの実装をやってみた。

とりあえず、アーキテクチャは以下のようにした。

合成は旨く行った。

リソースの使用状況はこんな感じになった。

今回のRTLではUARTも入れているが必須ではない。また、iCE40LMはI2CとSPI IPをハードマクロで内蔵しているので、これらを利用すれば、リソース的には余裕が出来る筈だ。