この土日はあまり時間がとれなかったので、Standard FormatとExtend FormatのArbitration、Standard Format同士のArbitration、DLC(Data Length Code)を見た。

(Extend Fromat同士のArbitrationは既に検証済み)

Arbitrationに関しては何れも問題なく動作したが、波形的には従来見ているものと大差ないので、

今回はDLCについて書く。

CAN では1 Frame当たり0~8 Byte迄のDataを転送できるが、その転送長はCONTROL FIELD内

の4bitのDLC(Data Length Code)で表す。

転送長とDLC各bitとの対応は上記のとおりである(Dを0、Rを1と見れば普通のBinary表現)が、

転送長が0~8の9種であるのに対してDLCは2^15 = 16通りある。

CAN では8以上は8と解釈することになっている。(CAN Specification 2.0 Addendum page 1)

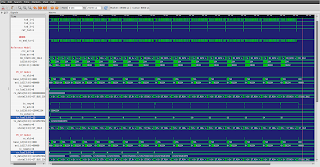

上図はDLCを0~15迄振ってNode1から送信をした場合であるが、DLCが8以上では転送長は8に丸められている。

上図はRemote frameでDLCを0~15にした場合だ。

Remote frameはData転送を要求するFrameなのでRemote Frame自体にはData転送は無い。

従って、DLC0~15の各Frameの長さは同一になっているのが判る。