camera i/f (cif)とvideo timing生成部、dvi_enc (dvi encoder)部の組み込みまでできた。

clockは、cif部は25MHz、内部bus (memory i/f)は65MHz、ddr2 i/fは140MHz、dvi_encは325MHzだが全てmetしている。

dvi_encはshift registerからODDRに至る経路でtimingが満たせなかったため、repeater用のF/Fを2段追加した。repeater用のF/Fは元々入れてあった物と合わせて3個入れたことになる。

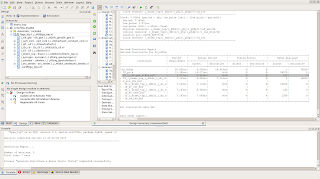

←planAheadでその内の1つの経路を確認した。(赤色の経路)残念な事にその内の2個は1つのSLICEに割り当てられており、repeaterの役を果たしていない。配置制約をかければもっと少ないrepeater (F/F)数に出来そうな気もするが、可能な限り制約をかけるのは避けたいと考えているので、現状で良しとしよう。

まだline buffer部を入れていないのでdram→dvi への出力は出来ないが、cif→dramへの部分は入れてあるのでdramに取り込んだdataをuart経由で吸い上げることは可能な筈だが、ここはあせらず全てを組み込んでから動作確認に進もうと思う。

また、multiport i/fは3port (cif, video, uif)に増やすつもりだ。

0 件のコメント:

コメントを投稿