http://bravo-fpga.blogspot.jp/2014/10/zybo-6.html

が、時は過ぎvivadoの版も上がり、今時はdegilentからzyboのboardfileを入手してvivadoに追加すればtarget boardにzyboが選択できるようになっている。boardfileのインストールは定義ファイルをインストールディレクトリ下の/data/boards/board_filesに置くだけだ。preset parameterを変更するよりも簡単だ。そこで、ここらでboardfile方式に移行することにした。

boardfileはここから入手できる。

https://reference.digilentinc.com/reference/software/vivado/board-files

boardfileをインストール後以下のようにしてdesignを移行した。

まず、現行のprojectを開いてblock desginをexportした。

次に新しいproject用のフォルダを作成し、exportしたtclファイルをコピーした。

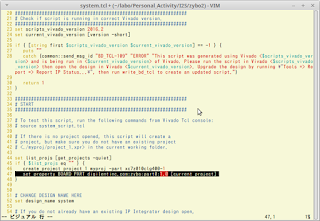

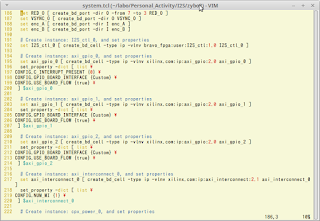

tclファイルを編集する。

preset parameterを指定している行を削除する。

create_projectしている部分に以下の様にzyboの情報を追加する。

gpioの定義の修正

exportされたtclでは何故かgpioの入出力とbit幅の定義が抜けているので、それを修正する。

修正前

修正後

vivadoを起動してprojectをcreateする。

Default partのページで素子名ではなくBoardsのZyboを選択する。

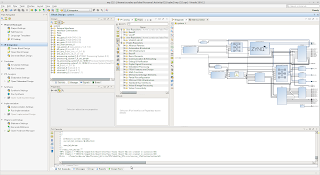

Create Block Designを実行してBlock Designerを開き、IP Repositoriesに自作IPのRepositoryを追加する。

tcl Consoleで先ほど編集したsystem.tclをsourceするとBlock Designが実行される。

構築が終わったら、Generate Block Designを実行後、HDL Wrapperを生成する。

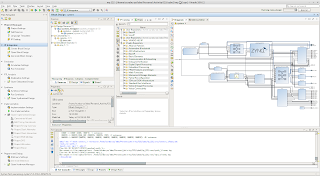

これでBlock Designが出来たので、Run Implementationボタンをクリックして合成、Inplementationまでを実行、最後にGenerate BitstreamしてBitsteramを生成

おっと、制約ファイルを取り込むのを忘れていた。

元のprojectのxdcファイルを新しいprojectにloadする。

気を取りなおして、Run Implementationからretry

タイミングはMetした。入出力遅延を設定していないピンがあるため、Check Timingに!マークが付いてはいるが。

Generate Bitstreamを実行してBitstreamの生成まで完了した。