このブログで作成したI2Sコントローラのデザインでは、I2S IPの出力をDFT(離散フーリエ変換)して、スペクトルをDVIに出力している。

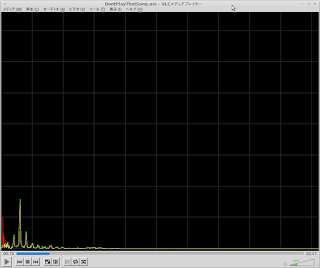

以下はDVI出力を録画してVLCメディアプレイヤーで再生した画像である。

以下はI2SコントローラのvivadoのブロックデザインのDFT IP部である。

dft_coreでDFTされたスペクトルデータは単精度浮動小数形式の複素数で出力(sfp_rが実部、sfp_iが虚部)される。 cpx_powerで複素数を16bit整数形式のパワースペクトルに変換し2ポートRAMにバッファする。 vif(video interface module)は自分のタイミングでその2ポートRAMからデータを読出してDVIに出力する。

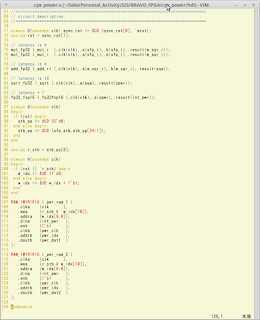

以下はcpx_powerのverilog ソースである。

浮動小数の加算、乗算、√の演算器はISEのCORE Generatorで生成しそれをインスタンスした。

今回はこれをCで書き直しでvivado_hlsで合成してみることにした訳だ。

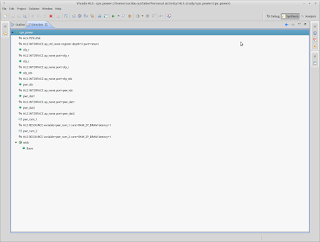

まず、以下のように記述してみた。ただし、この記述の場合バッファ読出し部のクロックが明示されていないという問題がある。

Directiveは以下のように定義した。

合成は成功した。

上記のとおり、現状の記述では全体として単一のクロックで動作する回路が生成されてしまうという問題がある。意図した回路を生成させるためには、関数をバッファの書込側と読出し側で別々に分けてスレッドとして記述し且つクロックも明示する等の工夫が必要なんじゃないかという気がしている。

2016.02.07 追記

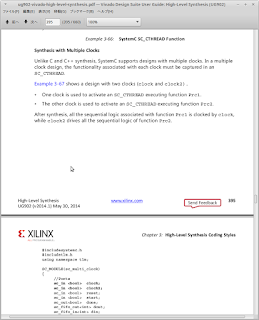

UG902 Vivado Design Suite User Guide High-Level Synthesis を見ると、複数クロックを使う今回のようなデザインはSystemCによるSC_THREAD記述しか方法が無いみたいだ。

しかし、SystemC で記述する時点で既に高位合成では無い気がする。そもそも、C及びC++にクロックという概念が無いので仕方ないのだろうけど、それを無理してSystemCで上記のように記述するんだったら、この部分はVerilogやVHDL等で記述したほうがマシだろうと思う。

ということで、全てをCで記述するのでは無くて、C記述とHDL記述を適材適所で用いて行くのが良いのかな?と思った。

0 件のコメント:

コメントを投稿