ここ数ヶ月、あまり考えないで部品や理工書を購入していたらえらい出費になってしまった。。。orz

しかし、なんで理工書ってのはこんなに高価なのかねー、、、学生や学校関係者ならば学割などで安く購入できる方法が使えるんだろうけど、あたしゃただのおっさんだもんなー。 (>_<) つらい。

どこかに、この50過ぎのおっさんにFPGA三昧の仕事をさせてくれる会社は無いものか・・・

FPGA三昧といってもFPGAを使ったボード開発とかだけど。ハードウェアやソフトウェアのスキルは公開しているRTLやこのブログの記事を見れば大体分かっていただけると思う。良くも悪くもこの程度しか無い。これ以外のスキルとしては、アナログ系回路も多少はできる。。。というか、本業ではこのところアナログ回路の設計開発が多い。あと、TOEICは10ヶ月位前のスコアで730点だった。 仕事のスタイルとしてはどちらかといえば単独でやるスタイルを好むがチームでの仕事も問題無い。ただし、やりたくないオーラ全開で能書きばかり垂れるような奴とのチームだけは勘弁して欲しい。こっちまでやる気が失せてしまう。 また、「あいまい耐性」はある方だと思う。

んーーー、まっ! 多少はねーー、多少はCNWな面もあるかも知れませんよそりゃ。

CNW… ちょっと何言ってるかわかんねー、みたいな。。 50年以上も生きていりゃ考え方とかに癖とかついちゃいますから、白無垢状態でこれから何色にでも染まります、ってな訳には、そりゃー行きませんわ。。ってな事をこんなところに書いてても何にもならないか・・・

いま抱えている仕事を放り出すわけには行かないので、転職できるとしても来年の後半になるが。。

FPGA三昧の仕事がしたいなーー、どこかにいい転職先は無いものか・・・

話は変わって、ツイッターのタイムラインを見ていたら、DIPSYというiCE40Ultraを使ったDIP型のFPGAモジュールの開発プロジェクトの情報を見つけた。 オリジナルはEETimesの記事のようだ。

http://www.eetimes.com/author.asp?section_id=216&doc_id=1327108

この記事でリンクしている

リンク先に実物の写真も載っていた。。。 ちょっと親近感を覚えた。 でも、載っかっているFPGAはiCE40UL1Kなのでリソース規模は小さいし、ピン数も少ないので用途は限られてくる気がする。 フルカラーLEDの調光くらいなのかな? 用途としては。。。

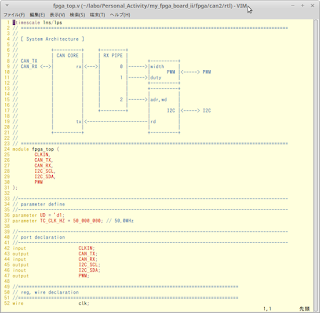

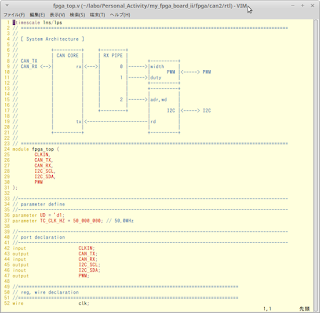

さて、うちの子(ボード)だが、以下のようなアーキテクチャを実装して動かしてみることにした。

PWMとI2Cマスタを持ち、CAN経由でそれらを制御してみる。

RX PIPEは受信フレームのIDフィールドをパターンマッチングして一致したフレームを各ポートに振り分ける。ポート0はPWMの周期設定、ポート1はDuty比設定、でこれらは標準IDフォーマットを使う。また、書込(マスター➔当FPGA)のみとする。 ポート2はI2Cの制御用で拡張IDフォーマットを使い、拡張IDの部分をレジスタインデックスとして使うようにした。リモートフレームによりリードバックも可能とする。

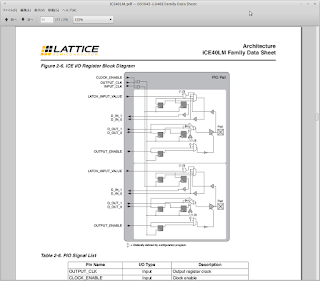

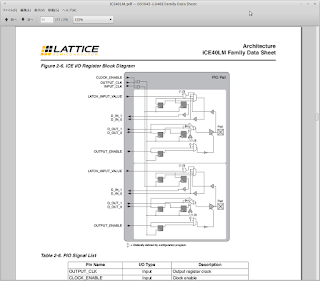

I2Cはハードコアを使わずに自作のI2C IPを使ってみた。 I2CのSDAはinout(双方向)でオープンドレインにする必要があるのだが、iCE40の開発環境ではオープンドレインのRTL記述が出来ないらしくエラーとなってしまう。しかし、FPGAのIOBの構造的には可能な筈だ。

そこで、シミュレーション用ライブラリソース等を参考にして上記のようにSB_IOをインスタンスして見た。合成は一見成功している。しかし、生成されたネットリスト(ゲートシミュレーション用ネットリスト)で確認すると、オープンドレイン出力の系は生成されているのだが何故か入力の系の回路が生成されていない。ネットリストを見るとRTLでインスタンスしたSB_IOはIO_PADとPRE_IOというモジュールに変わっており、PRE_IOのDIN0のポートが未接続となっている。

SB_IOの代わりに、IO_PADとPRE_IOでRTLを使ってみたのだが合成でエラーとなってしまう。。

なぜ、出来ないんだろう??

素直にI2Cのハードマクロを使ったほうがいいのかな…