リードデータのvalid信号はDQSBUFDのDATAVALIDを使わないで別に作ることにした。

rd_ren信号を(DQSBUFDのREADポートに入力する信号)をrpp[2:0]でシフトして生成している。

rd_renはDQSのプリアンブル分も含んだパルス幅になっていて必要な幅よりも広いため、rd_renを1サイクル遅延させたrpp[0]とrd_renとをANDしてrpp[1]に入れ、それをもう1段遅延させている。

DQSDLLB部も修正を行った。DQSDLLBはリード時にDQS信号の位相を90°ズラすためのハードマクロであるが、このモジュールのUDDCNTLN入力を常時 L にしていた。この信号は負論理の信号で、L が入力されると位相量が更新される。(この更新というのはDLLのキャリブレーションに相当する動作と思われる。) ハンドブックにはリード/ライト期間外に L にして更新できると書いてあった。つまり、リード/ライト時は L にしてはいけなかった。そこで、以下のようにした。起動時に自動で1回更新処理を行い、以降はソフトウェア制御により任意のタイミングで更新できるようにした。当然、この時はリード/ライトは発生しない状態にしておく必要はある。

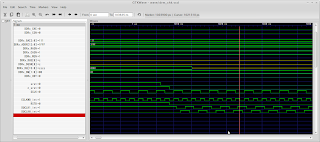

以上の変更&修正を行ったところ、リードでそれらしい値が読めるようになったが、微妙に違う。ただし、今度は10回リードしても値自体の変動は無かったので、おそらくライト側の異常が考えられた。実は、この症状には思いつくところがあった。以下はライトのシミュレーションの波形だが、赤丸部のようにグリッジが発生している。これは以前から気づいてはいたのだがシミュレーションモデルの問題だとばかり思っていた。が、実機でも実際にこの現象が発生しているのかも知れない。

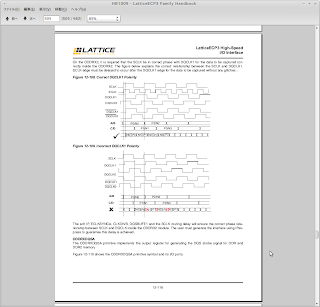

そこで、改めてハンドブックを調べてみたところ、ODDRX2Dに入力するSCLKとDQCLK1との位相関係について制約があることが判った。 SCLKとDQCLK1とは逆位相にする必要があるようだ。

このDQCLK0, 1はどこで生成されるかというと、DQSBUFDで生成される。

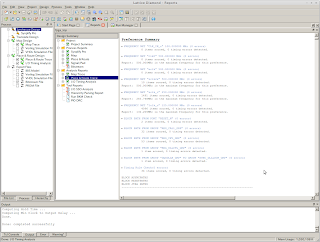

DQSBUFDにはSCLKも入力されるし、DQCLK0,1はハードマクロからハードマクロへの信号なのだから、特別はことをしなくても上記の位相関係をDQSBUFDが担保するべきでは?という気もするのだが。。。 そこで、DQSBUFDのシミュレーションモデルのソースを確認したところ以下のようになっていた。

入力であるECLKWB_int1はECLKW (ECLK) を遅延させた信号、RSTBはRST信号で、DQCLK0_int、DQCLK1_intが最終的にDQCLK0、DQCLK1になる。この記述からSCLKはまったく論理に絡んでいないことが判る。しかも、制御できる入力はRSTだけなので、この信号のタイミングを工夫して与えることで、SCLKとDQCLK1との位相関係を満たさなければならない。。。うーむ。

で、結局以下のようにRST信号をSCLKの立ち下がりエッジで叩いてからDQSBUFDに入力するようにした。(dc_ddrio内部でsrstがDQSBUFDのRSTに接続されている。)

ちなみに、DQCLK1とDQCLK0との位相関係について、上記のハンドブックの図ではDQCLK1の1の期間にDQCLK0が1になるようになっているが、おそらくこれは誤植と思われる。DQSBUFDのシミュレーションモデルのソースでは以下のような記述となっており、DQCLK0_intにはDQCLK1_intを反転した信号が入力されている。この記述ではDQCLK1、0は H → Hというような位相関係にはならない。

RSTの修正を行った結果、USB-UART経由での単発のアクセスによる確認ではあるが、正常にリード/ライトできるようになった。次はLFSR等による高密度なアクセスによる確認をする必要がある。が、その前に、500MHz (1Gbps)で動くかどうか確認してみた。各部の動作周波数は以下のようになる。

合成は成功した。

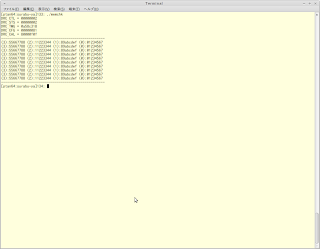

以下のような簡単なプログラムで動作確認してみた。

結果はOK

次に以下のようなプログラムで動作確認してみた。リードバック動作を伴うこととUSB-UARTの通信速度の遅さもあって、このプログラムの実行は一晩を要したが、エラーなく最後まで動作していた。

ということで、1Gbpsでの動作も可能なようだ。。。すばらしい。Lattice すげー

このLatticeECP3 Versa Development Kitは買って正解だったかも知れない、うんうん。

ネットで検索してみてもLatticeのFPGAで××を作った的なページは殆ど見つからない。検索のしかたが悪いのかも知れないが。 開発環境であるDiamondの習得はそれほど難しくないと思う。むしろ簡単な部類に入るんじゃ無いだろうか。タイミングアナライザ等は操作中に突然落ちたりすることがあるが、以前(Lattice XP2で何かを作っていた頃)に比べれば頻度は少ない。それにLinux版特有の症状かも知れないし。デバイスの価格も安そうだし、もっと人気があっても良さそうな気がするが。。。まぁ、DQSBUFDのように癖のあるハードマクロが有ったりはするが、慣れればどうということも無いんじゃなかろうかとも思う。。。今のところは。。。それに、DRAM-PHYはIPExpressで生成して使うだろう普通は。っという気もする。であるなら、やはり、もっと普及してもいいよな。私が知らないだけか?