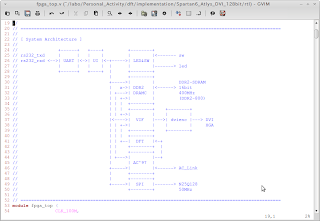

現状のSystem Architectureは以下の通り。

AC97コントローラの再生のRchをDFTに入力し、DFTの出力をDRAMを介さず、直接VIF(フレームバッファ)に入れている。 VGAの表示サイズがXGA (1024x768)で横方向がDFTの出力データ数と一致するので、VIFのsyncgenのxadr(水平方向カウンタ)の値をDFTのpramのアドレス入力として与え、その出力をsyngenのyadr(垂直方向カウンタ)の値と比較して、hitした場合に赤、hitしない場合に黒を出力するようにして、スペクトル表示を行うようにした。

以下はDFTの当該部だ。

また、以下はVIFの当該部だ。

この構造で音楽データを再生させながらスペクトル表示させて見たところ、再生終了(音量がゼロ)後もスペクトルが残ったり、また、そのまま放置しておいても、スペクトルが徐々に増加したりといった現象が見られた。どうも、演算誤差の累積が原因のようだ。 そこで、とりあえず、データ入力2048点毎にアキュムレータの値をクリアするようにして、動作確認を進めてみることにした。これは2048点毎にDFTを実行することと同じことになるが、この回路の設計思想からは外れるので、誤魔化しではある。dft_coreの当該部を以下に示す。 165行目のscntでデータをカウントし、2048個に到達するとsclrが1になり、アキュムレータRAMからのリード値を0に置き換えている。(180,181行目)

回路規模だが、現状 dft_core部は以下の通りだ。

dft_core部の中身はDFT演算のみであり、絶対値演算と平方根、対数変換はdft_powerという別のモジュールで行う。この、dft_power部の回路規模は以下のようになった。

現状、浮動小数演算器はハードウェア乗算器(DSP48)を使わない構成で生成しているため、LUTの使用量が大きくなっている。

dft_top (dft_core + dft_power)部としての規模は以下のようになった。

これまでの数値は、論理合成結果なので、マッピング後の結果とは若干違ってくるかも知れない。

また、何とかこれをSpartan3E 250Eにも入れられないかとやってみたのだが、駄目だった。

ムググッ、おのれ250Eめ、今度固定小数方式でリベンジしてやる。

(その前に、誤差問題を対応する必要があるが。)

Spartan6 xc6slx45への、全体の合成・マッピングは出来て、タイミングもMetした。

で、データを再生して表示してみた。

これの対数変換による表示は以下だが、ちょっとパッとしない。

今度はテンポの早いやつをやってみた。

これで、誤差問題が解決すればもっとおめでたい。

DFT演算ではexp(2πf/N)を乗じているので、ベクトルを常時回転させていることに相当するが、入力がゼロでもスペクトル値が増加すると言うことは、演算誤差により回転時に外側に膨らんでいっていると考えられる。だから、内側への補正が出来れば解決出来そうな気がするのだが、、、要検討だ。

げっ!、もうこんな時間だ。寝なきゃ。

0 件のコメント:

コメントを投稿