AC97 Codec用のコントローラは大体出来たので、次にオーディオ帯域用のスペクトルアナライザを作って見たくなった。スペクトルアナライザと言えば、おそらくFFT方式が常套手段だと思うが、今回はDFT (Discrete Fourier Transformation)方式でやってみることにした。

ここで、信号Xnについて、信号は-∞から+∞へ連続している信号列と定義し直す。

そして、(1)式を、任意のp点からp+(N-1)までの区間の信号列に対して行うように書き直す。

となる。。。。 うほっ、、、これは面白い。!!

この式は、直前のスペクトル値を用いて回帰的に計算すれば、exp(2πf/N)の乗算だけで済むことを表している。乗算・加減算の回数も(1)式に比べてかなり少なくなる。

ここまでの式では、p点からp+(N-1)までの信号を用いて、p点のスペクトルを計算するという表現になっていたが、これだと未来の信号を用いて現在の値を求めるような形になり、少々気持ち悪い。

そこで、過去のN点から現在の値を求める形式に書き直す。

念のため、C言語のプログラムを作成してシミュレーションしてみた。

プログラムは以下のとおり。

32~41行で入力信号を作成している。以下に波形を示す。

0~1024の区間はx1、x128倍、x256倍の周波数の合成波で、2048~3062の区間はx64倍の周波数の信号だ。従って、処理の初めのほうでは、スペクトルはx1,x128,x256の3箇所で観測され、次にx64で観測され、最終的にはスペクトルは観測されなくなる筈だ。

上記プログラムの出力から、各サンプル毎のスペクトルをgnuplotで描画・出力し、avidemuxでこれらを合成して、動画を作成した。このアルゴリズムをFPGAに実装して、上記のような信号列を入れれば以下のようなスペクトル波形が得られるはずだ。

うほほっ、、、面白い。 ちゃんと周波数領域に変換できている。

この方式だと、コンパクトな回路が出来そうだ。

使用周波数帯は、オーディオ帯域用を考えているが、これに対してFPGA内部が100MHzでの動作となるので、例えばオーディオのサンプリングレートが48KHzの場合速度比は2083倍になるので、1サンプル毎に2048点程度のDFTは楽勝で出来そうだ。

スペクトル全体を求める式は(2)式風に書くと、以下のように書ける。

ここで、正弦波形の対称性を考慮すると、

なので、(9)式は以下のようにも出来る。

つまり、exp(2πf/N)部は1/4象限分のみ持てばよくて、かつ、演算部を4並列することで、1サンプル以内の点数を4倍に増やせる。したがって、回路規模は若干大きくなるがこの方法でやれば8192点程度は出来そうだ。

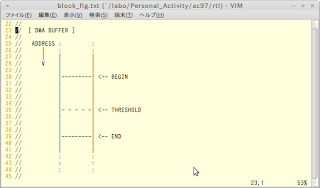

それでは、RTL作成に進もう。